Нейрочипы и нейрокомпьютеры

Вместе с тем сеть способна обобщать схожие образы, относя их к одному классу. Тестирование обученной сети позволяет определить топологию классов в выходном слое.

Для приведения откликов обученной сети к удобному представлению сеть может быть дополнена еще одним слоем, который в процессе обучения по алгоритму обучения однослойного перцептрона [32] позволяет отображать выходные реакции сети в требуемом представлении.

Другой алгоритм обучения без учителя - алгоритм Кохонена - предусматривает подстройку синапсов на основании их значений от предыдущей итерации.

-\) + а\уГп -\)\. (1.41)

Из вышеприведенной формулы видно, что обучение сводится к минимизации разницы между входными сигналами нейрона, поступающими с

выходов нейронов предыдущего слоя , и весовыми коэффициентами его синапсов.

Полный алгоритм обучения имеет примерно такую же структуру, как в методах Хебба, но на третьем шаге из всего слоя выбирается нейрон, значения синапсов которого максимально походят на входной образ, и подстройка весов по формуле (1.41) проводится только для него. Эта так называемая аккредитация может сопровождаться затормаживанием всех остальных нейронов слоя и введением выбранного нейрона в насыщение. Выбор такого нейрона может осуществляться, например, расчетом скалярного произведения вектора весовых коэффициентов с вектором входных значений.

Максимальное произведение дает выигравший нейрон.

Другой вариант - расчет расстояния между этими векторами в р -мерном пространстве (1-42)

где p - размерность векторов, j - индекс нейрона в слое п , і - индекс суммирования по нейронам (н-І)-го слоя, w;/ - вес синапса, соединяющего нейроны; выходы нейронов (л-І)-го слоя являются входными значениями для слоя п . Корень в формуле (1.42) брать не обязательно, так как важна лишь относительная оценка различных D. .

В данном случае, побеждает нейрон с наименьшим расстоянием. Иногда слишком часто получающие аккредитацию нейроны принудительно исключаются из рассмотрения, чтобы уравнять права всех нейронов слоя.

Простейший вариант такого алгоритма заключается в торможении только что выигравшего нейрона.

При практическом использовании для обучения алгоритма Кохонена, как правило, осуществляется нормализация входных образов. При этом на стадии инициализации осуществляется нормализация начальных значений весовых коэффициентов

где хі - і -я компонента вектора входного образа или вектора весовых коэффициентов, ап- его размерность. Такой подход позволяет сократить длительность процесса обучения.

Инициализация весовых коэффициентов случайными значениями может привести к тому, что различные классы, которым соответствуют плотно распределенные входные образы, сольются или, наоборот, раздробятся на дополнительные подклассы в случае близких образов одного и того же класса. Для избежания такой ситуации используется метод выпуклой комбинации [81]. Суть его сводится к тому, что входные нормализованные образы подвергаются преобразованию;

(1.44)

где xt - і -я компонента входного образа, а п - общее число его компонент, a(t) - коэффициент, изменяющийся в процессе обучения от нуля до единицы, в результате чего вначале на входы сети подаются практически одинаковые образы, а с течением времени они все больше сходятся к исходным. Весовые коэффициенты устанавливаются на шаге инициализации равными величине

(1.45)

где п - размерность вектора весов для нейронов инициализируемого слоя.

На основе рассмотренного выше метода строятся нейронные сети особого типа - так называемые самоорганизующиеся структуры - selforganizing feature maps. Однако речь идет не об изменении структуры сети, а только о подстройке синапсов. Для них после выбора из слоя п j -го

нейрона с минимальным расстоянием Dj обучается по формуле (1.41) не

только этот нейрон, но и его соседи, расположенные в окрестности R . Величина R на первых итерациях очень большая, так что обучаются все нейроны, но с течением времени она уменьшается до нуля. Таким образом, чем ближе конец обучения, тем точнее определяется группа нейронов, отвечающих каждому классу образов.

Другим распространенным методом обучения без учителя является обучение методом соревнования. В отличие от правила обучения Хебба, в котором множество выходных нейронов могут возбуждаться одновременно, при соревновательном обучении выходные нейроны соревнуются между собой за активизацию.

Это явление известно как правило победитель берет все. Подобное обучение имеет место в биологических нейронных сетях.

Обучение посредством соревнования позволяет кластеризовать входные данные: подобные примеры группируются сетью в соответствии с корреляцией и представляются одним элементом.

При обучении модифицируются только веса победившего нейрона. Эффект этого правила достигается за счет такого изменения сохраненного в сети образца (вектора весов связей победившего нейрона), при котором он становится чуть ближе к входному примеру.

Необходимо заметить, что сеть никогда не перестанет обучаться, если параметр скорости обучения не равен нулю. Некоторый входной образец может активизировать другой выходной нейрон на последующих итерациях в процессе обучения. Это ставит вопрос об устойчивости обучающей системы. Система считается устойчивой, если ни один из примеров обучающей выборки не изменяет своей принадлежности к категории после конечного числа итераций обучающего процесса.

Один из способов достижения стабильности состоит в постепенном уменьшении до нуля параметра скорости обучения. Однако это искусственное торможение обучения вызывает другую проблему, называемую пластичностью и связанную со способностью к адаптации к новым данным.

Эти особенности обучения методом соревнования известны под названием дилеммы стабильностшпластичности Гроссберга [6].

Кроме рассмотренных, следует упомянуть некоторые другие алгоритмы: Adaline и Madaline, линейный дискриминантный анализ, проекции Саммона [14], анализ главных компонентов [74].

Необходимо отметить, что обучение без учителя гораздо более чувствительно‘к выбору оптимальных параметров, нежели обучение с учителем. Во-первых, его качество сильно зависит от начальных весовых величин синапсов. Во-вторых, обучение критично к выбору радиуса обучения и скорости его изменения. И, наконец, разумеется, очень важен характер изменения собственно коэффициента обучения.

В связи с этим потребуется провести предварительную работу по подбору оптимальных параметров обучения сети.

Несмотря на некоторые сложности реализации, алгоритмы обучения без учителя находят обширное и успешное применение. Например, в [6] описана многослойная нейронная сеть, которая по алгоритму самоорганизующейся структуры обучается распознавать рукописные символы. Возникающее после обучения разбиение на классы может в случае необходимости уточняться с помощью обучения с учителем.

По сути дела, по алгоритму обучения без учителя функционируют и наиболее сложные из известных на сегодняшний день искусственные нейронные сети - ког-нитрон и неокогнитрон, максимально приблизившиеся в своем воплощении к структуре мозга. Однако они, конечно, существенно отличаются от рассмотренных выше сетей и намного более сложны.

Тем не менее на основе вышеизложенного материала можно создать реально действующие системы для распознавания образов, сжатия информации, автоматизированного управления, экспертных оценок и других приложений.

Нейрочипы и нейрокомпьютеры

Быстрое развитие и постоянно расширяющееся внедрение нейроссте-вых методов и алгоритмов как в коммерческие так и в военные приложения способствует росту устойчивого интереса к созданию средств аппаратной реализации нейрокомпьютерной (НК) технологии. Прежде всего это относится к разработке функционально сложных сверхбольших интегральных схем (СБИС) со специализированной структурой, которая ориентирована на аппаратную реализацию одной или нескольких наиболее часто используемых парадигм нейронных сетей.

Общее определение нейрокомпьютера может быть сформулировано следующим образом [12]. Нейрокомпьютер - это вычислительная система с архитектурой аппаратного и программного обеспечения, адекватной выполнению алгоритмов, представленных в нейросетевом логическом базисе.

Системы, созданные на стандартной микропроцессорной элементной базе могут являться эффективными программными эмуляторами нейросе-тевых алгоритмов. Однако программная эмуляция нейросетевых алгоритмов на вычислительных средствах, реализованных на элементной базе, не имеющей отношения к нейросетевому логическому базису, скорее всего, является временным явлением.

Для аппаратной реализации таких алгоритмов эффективнее создавать архитектуры, выполняющие операции в нейросетевом базисе - на основе логической сети нейронов при полном отказе от булевских элементов типа И, ИЛИ, НЕ.

Ограничиваясь проблемами использования в современных разрабатываемых устройствах НС и НК полупроводниковых технологий, можно выделить следующие трудности возникающие при их создании: высокая структурная сложность и низкая надежность систем; практическая трудность реализации архитектур обучения, самообучения, самоорганизации НС для непрерывно изменяемых весов взаимодействия нейронов;

технологические сложности изготовления сверхинтегрированных НС и НК на нейрочипах и субсистемах кремний на пластине;

увеличение потребляемой мощности и потеря системного быстродействия в субсистемах НС по мере увеличения степени их интеграции.

Выбор эффективного типа нейрокомпьютера для решения конкретной задачи или конкретного класса задач рекомендуется производить в определенной последовательности [10].

На первом этапе в общепринятых терминах формулируется математическая постановка задачи.

На втором этапе осуществляется переформулировка задачи в терминах системной постановки, требуемой для ее решения на нейрокомпьютере. При этом должно быть выделено "нейронное ядро" задачи, т. е. часть задачи адекватная нейронному базису.

Для более эффективного использования нейрокомпьютеров это ядро должно составлять основную, как можно большую, долю множества операций в алгоритме, представляющем собой общую математическую формулировку задачи.

На третьем этапе для части алгоритма задачи, представляющего нейронное ядро, формулируются основные характеристики системной постановки задачи:

входной сигнал; выходной сигнал; желаемый выходной сигнал; структура разомкнутой системы; ошибка системы;

функционал оптимизации системы; градиент функционала оптимизации;

алгоритм настройки системы в процессе решения задачи;

замкнутая система.

На четвертом этапе для системной постановки конкретной задачи заказчика производится подсчет необходимых ресурсов ее решения в структурных термйнах НС: число эмулируемых нейронов; число эмулируемых связей; число переключений связей в процессе решения задачи нейронным ядром алгоритма.

Пятый этап требует проведения моделирования процесса решения задачи на ПЭВМ.

На шестом этапе производится оценка производительности НК на конкретной задаче с выбором конкретной технологии реализации.

Примеры существующих нейрокомпьютеров в порядке увеличения их производительности следующие [9]:

программная эмуляция на однопроцессорной ЭВМ;

транспьютерная реализация различной конфигурации транспьютерной сети;

реализация нейронной архитектуры на стандартных микропроцессорных СБИС;

реализация на аналоговых и аналого-цифровых СБИС;

реализация на оптоэлектронных СБИС;

реализация на пластине.

Несмотря на всплеск исследований и разработок полупроводниковых, оптических, оптоэлектронных, магнитоэлектронных, биомолекулярных НС и НК, вопрос выбора приоритетных и наиболее конкурентоспособных направлений до сих пор открыт.

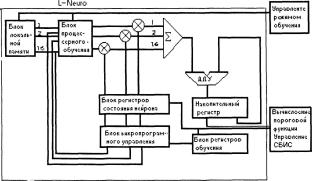

Разработка функционально сложных СБИС со специализированной структурой, ориентированной на аппаратную реализацию одной или нескольких наиболее часто используемых парадигм нейронных сетей привела к созданию параллельных нейросетевых ускорительных плат для различных базовых вычислительных платформ. Примером такой реализации является разработка фирмой Telmat (Франция) нейросетевой ускорительной платы на базе специализированной СБИС L-Neuro [22, 52, 89].

СБИС L-Neuro цифровая каскадируемая схема для моделирования дискретных нейросетевых алгоритмов, выполненная по 1,5 мк КМОП-технологии. Она совместима с интерфейсом памяти транспьютера фирмы Inmos и аппаратно реализует палаллельное выполнение базовых нейросетевых оппераций в режимах распознавания и обучения для нейрона, имеющего 16 входов и один выход. Наличие локальной памяти весовых коэффициентов объемом 1 Кбайт с произвольной выборкой, и 32-байтного регистра состояния нейронов, обеспечивает возможность моделирования нейросетевых структур от фрагментов из 32 нейронов с 32 бай-36

товыми входами до фрагментов из четырех нейронов с 256 битовыми входами. Эффективную реализацию различных нейросетевых парадигм и правил обучения обеспечивает набор из 47 команд СБИС L-Neuro.

В составе СБИС L-Neuro можно выделить следующие структурные

элементы:

массив локальной памяти весовых коэффициентов (Sunaptic RAM). Время доступа к памяти со стороны внешних устройств (по адресной мультиплексной шине транспьютера) составляет 150 нс;

два блока регистров состояния нейрона (Neural State Register (NSR)). В каждом блоке содержиться 16 универсальных байтовых регистров, обеспечивающих хранение и модификацию в синхронном и асинхронном режимах значений выходов нейронов;

блок процессоров и регистров обучения (Learning Register), содержащий 16 регистров, каждый из которых обеспечивает хранение, а также выполнение операций сложения и вычитания 16-битовых операндов, представляющих собой значения весовых коэффициентов.

блок умножителей, состоящий из 16 схем умножения байтового операнда на бит (AND). С помощью данного блока вычисляются элементарные произведения для нахождения взвешенной суммы.

блок накопительного сумматора, обеспечивающий сложение частных сумм и накопление результата в накопительном регистре, в случае вычисления выходного значения нейрона, имеющего более 16 входов, или значения выхода более 1 бита;

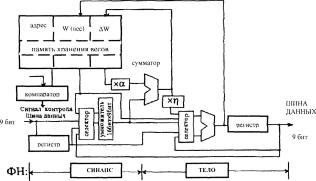

блок дешифрации команд и микропрограммного управления, обеспечивающий выполнение 19-разрядных команд и микропрограмм. Структурная схема СБИС L-Neuro представлена на рис.

1.12.

Рис. 1.12. Структурная схема СБИС L-Neuro

СБИС L-Neuro имеет два основных режима функционирования: обучение и распознавание (раскодирование). Выполнение вычислительных операций в данных режимах осуществляется с помощью микропрограммного управления.

Кроме того, предусмотрено выполнение отдельных функций вычислительного процесса с помощью задания управляющих параметров, размещаемых на специально выделенных регистрах управления.

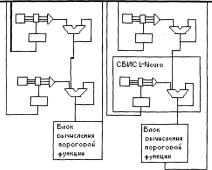

СБИС L-Neuro является основным блоком, на базе которого могут создаваться различные параллельные нейровычислительные ускорительные платы и супернейрокомпыотеры. Высокая степень параллелизма, естественно присущая нейросетевым алгоритмам, и каскадируемость СБИС L-Neuro обеспечивают возможность произвольного наращивания числа процессоров для достижения требуемой вычислительной мощности. Межпроцессорные взаимосвязи могут быть организованы в зависимости от функционального назначения и моделируемых нейросетевых парадигм. Структура взаимосвязи четырех СБИС L-Neuro для моделирования полносвязной сети приведена на рис.

1.13.

На базе СБИС L-Neuro в настоящее время разработано два типа плат: ускорительная плата для IBM PC совместимых компьютеров, содержащая 1 управляющий транспьютер, 4 СБИС L-Neuro, 128 Кбайт RAM;

ускорительная плата для вычислительной системы Т-Node Computer фирмы Telmat Multinode, содержащая 1 управляющий транспьютер, 4 СБИС L-Neuro и 4 Мбайт RAM.

Рис. 1.13. Структура взаимосвязи четырех СБИС L-Neuro для моделирования полносвязной сети

Одним из способов реализации НС в виде СБИС является использование приборов с зарядовой связью (ПЗС). И хотя данный способ имеет существенный недостаток - низкое быстродействие серийных ПЗС, в настоящее время разработано несколько схем, свидетельствующих об успешной конкуренции реализованных на ПЗС нейронных сетей при решении некоторого класса задач [113]. Так, например, решение задач распознавания образов не требует значительного быстродействия, но предполагает увеличение размерности НС и объема обрабатываемой информации.

ПЗС могут удовлетворить эти требования, так как, кроме отмеченного выше недостатка, они имеют и целый ряд преимуществ перед другими способами реализации.

Во-первых, элементарная ячейка ПЗС (МОП/МНОП конденсатор) имеет минимальные топологические размеры, и следовательно возможно создание СБИС с наивысшей степенью интеграции.

Во-вторых, ПЗС могут обрабатывать как аналоговую, так и цифровую информацию с одинаковым быстродействием.

В-третьих, при использовании ПЗС со скрытым каналом, передачу информации возможно осуществлять параллельно по нескольким слоям. Таким образом, по сравнению с другими способами реализации ПЗС имеют повышенное быстродействие.

В-четвертых, использование ПЗС детекторов во многом снимает ограничения связанные с конечным числом выводов микросхем, что снижает время необходимое на инициирование системы.

Кроме того, использование ПЗС позволяет создавать приборы, совместимые с любым другим способом реализации НС. Однако, как уже было отмечено, применение ПЗС для реализации НС возможно только в том случае, если данная элементная база удовлетворяет условиям конкретной решаемой задачи.

Использование субмикронных технологий и минипроизводств, новых схемотехнических и системотехнических принципов построения маломощных сверхбыстродействующих ультраБИС (УБИС) позволило японской фирме Hitachi в 1990 г. разработать и изготовить НС на кремниевой пластине диаметром 5 по 0,8-микромстровой КМОП-технологии [7]. Пластина была смонтирована на керамической подложке 15x15 см. На этой кремниевой пластине было размещено 19 млн.

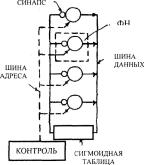

МОП-транзисторов в 64 нейрочипах. Такие БИС, использованные в качестве базовой ячейки на пластине, позволяли создать НС из 576 формальных нейронов (ФН) и 36 864 синапсов.

В применяемом базовом матричном кристалле (БМК) размером 12x12 мм было размещено 12 ФН. Каждый нейрон представлялся 1000 КМОП-элементами с памятью 64 слова по 18 бит.

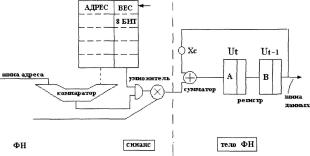

На рис. 1.14 представлена цифровая НС на пластине, эквивалентная сети Хопфилда, на основе архитектуры шины с разделением времени [7].

Рис 1.14. Структурная схема НС, эквивалентной сети Хопфилда, с использованием шины данных с разделением времени

На рис. 1.15 дана схема ФН, функционирование которого описывается стандартными выражениями и реализуется с помощью стандартных булевых элементов и ячеек памяти [7].

Рис. 1.15. Структурная схема формального нейрона, реализованного с помощью стандартных булевых элементов и ячеек памяти

Предложенная архитектура шины данных позволяет резко сократить число соединений между ФН внутри и вне нейрочипа. Весовые коэффициенты ФН изменяются в диапазоне 8 бит, выходные сигналы кодируются 9-битовыми числами (см. рис.

1.14), а шина с разделением времени обеспечивает асинхронный обмен данными между ячейками (см. рис. 1.15).

НС на пластине может быть достаточно просто соединена с управляющим внешним компьютером и использована для широкого спектра интеллектуальных задач в рамках высокоорганизованных систем искусственного интеллекта. Например, задача коммивояжера для 16 городов была решена с помощью созданных НС и НК, работающего с временным циклом 267 мкс, за 0,1 с, причем скорость вычисления и решения подобных задач превышала на порядок возможности суперкомпьютера фирмы Hitachi произво-дительностью свыше миллиарда операций в секунду [7].

Затем в 1992-1993 гг. в рамках использования эффективной архитектуры шины данных с разделением времени (см. рис. 1.14) разработчики фирмы заложили в проектируемые НС возможности обучения и самообучения. Такая возможность появилась в измененной схеме всех используемых в НС новых ФН за счет дополнительной подстройки весовых коэффициентов (рис.

1.16).

Рис. 1.16. Модифицированная структурная схема формального нейрона с возможностью обучения и самообучения за счет дополнительной подстройки весовых коэффициентов

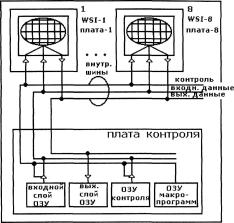

На рис. 1.17 представлена структура полной синтезированной НС с управляющей высокопроизводительной рабочей станцией, которая контролирует функционирование и необходимые операции всей системы.

Плата контроля накапливает и сохраняет данные входных и выходных слоев и базовой микропрограммы для последовательности обучающих шагов.

Сегодня уже имеется впечатляющая демонстрация возможностей трехмерных систем искусственных многослойных обучаемых перцеп-тронных НС, реализованных на пластинах, с оценкой общей производительности системы в классе распознавания образов в 24 биллиона переключении/с [50].

Наиболее изученный мощный адаптивный алгоритм для обучения многослойных персептронных НС - метод обратного распространения, использованный в 3D-HC, имел производительность 1,1 биллиона пе-рсключснии/с для матричного воплощения элементарных процессов 128x128 и давал оценку более впечатляющего качества трехмерных систем ближайшего будущего для матричного воплощения 512x512 около 54 биллионов переключении/с [50].

Рис. 1.17. Структурная схема нейросети на кремниевых пластинах с управляющей высокопроизводительной рабочей станцией, контролрующей функционирование и необходимые операции всей системы

Потенциальная возможность быстрого обучения, переобучения, самообучения НС вместе с высокими скоростными характеристиками обработки информации (зависящими от плотности представления собственно нейрона перспективного типа, его быстродействия и т.д., а также числа нейронов в НС, т. е. от уровня интеграции 3D-HC) является основным залогом возможности быстрого и качественного решения задач распознавания образов и сцен в реальном масштабе времени с большим числом имеющихся параметров. Более того, плотно упакованные системы из ЗО-НС, построенные из одинаковых элементов с определенной избыточностью, позволяют весьма эффективно выходить из ситуации локальной неработоспособности отдельных элементов или фрагментов НС за счет

дополнительной перестройки соответствующих весов еще работающих элементов так, что, хотя и с потерей в точности, надежности и системной скорости, НС будет продолжать функционировать.

При уменьшении линейных размеров линий связи (ЛС) до 1 мкм и в субмикронной области -для увеличения плотности компоновки систем, резко ухудшается их функционирование из-за возрастания сопротивлений ЛС, связанного с этим резкого возрастания времени распространения в них сигнала, а также из-за уменьшения срока службы ЛС вследствии электромиграции и других нежелательных эффектов (например, термических). связанных с высокими плотностями тока в ЛС. Поэтому оптимальным и наиболее кардинальным выходом из ситуации, обусловленной отказом длинных межсоединений на пластине и в ЗО-системах, является переход к чисто оптическим связям между чипами (в отдаленной перспективе и внутри чипа), несмотря на казалось бы избыточную необходимость преобразования электрических сигналов в оптические, и, наоборот, в 3D-HC.

Использование оптических связей в симбиозных ЗО-оптомикро-электронных НС позволяет:

увеличить уровень интеграции и системного быстродействия систем;

получить максимальную быстроту передачи информации, ограниченную скоростью света;

повысить помехоустойчивость Л С и системы в целом;

увеличить срок службы за счет увеличения надежности системы;

повысить эффективность возможности параллельного ввода, передачи и обработки информации.

В то же время обработка больших массивов информации в реальном масштабе времени в будущих оптомикроэлектронных 3D-HC обостряет проблему создания сверхбыстродействующих микроминиатюрных оптоэлектронных компонент, совместимых с субмикронными КМОП, КБИЛБИКМОП-элсмснтами на кремниевых пластинах. К середине 90-х годов все более широкое внимание стало уделяться гибридной Si-GaAs-технологии применительно к 2D- и 3D-HC [7] с усовершенствованием методов и средств интеграции на кремниевой подложке оптоэлектронных приборов (излучателей, модуляторов, фотоприемников) на основе слоев GaAs и традиционных микроэлектронных компонентов: п-МОП, р-МОП, п-р-п, р-п-р транзисторов, резисторов, емкостей, созданных в рамках субмикронных кремниевых технологий.